Departament de Microelectrònica i Sistemes Electrònics

AVR i FONAMENTS DE COMPUTADORS

Enginyeria en Informàtica (ETSE)

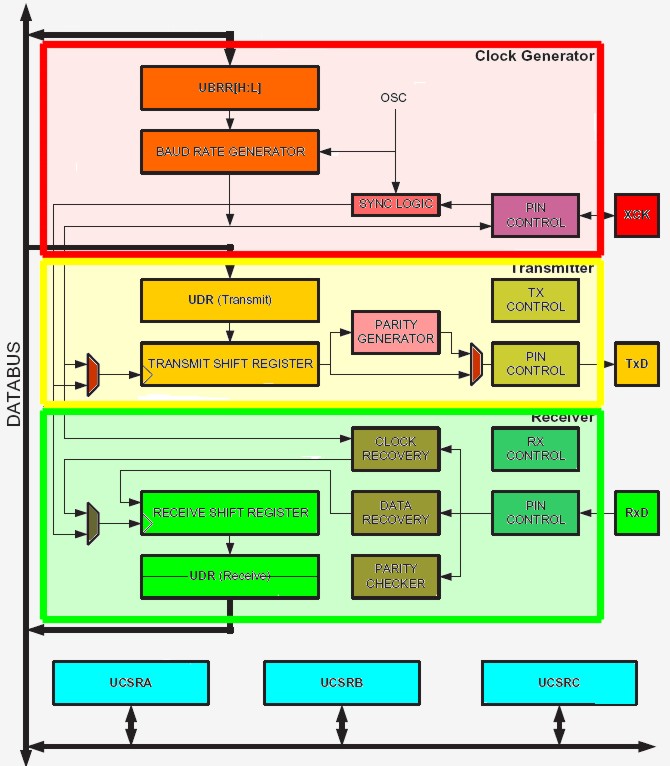

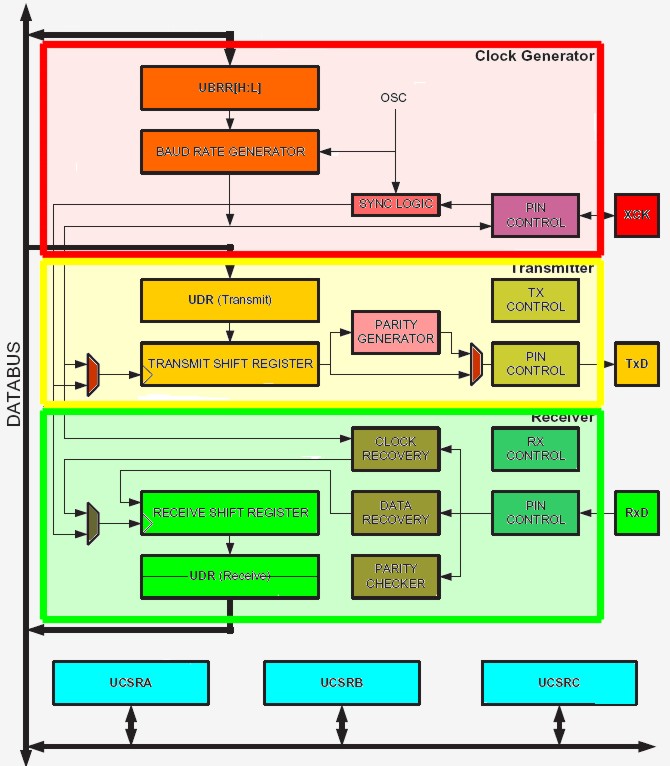

Arquitectura de la UART

El microcontrolador ATmega8 disposa d'un mòdul de transmissió/recepció sèrie síncron/asíncron (USART) amb característiques com:

- Full dúplex. Té registres de transmissió i recepció independents que el permeten enviar i rebre al mateix temps

- Comunicació amb múltiples baudrate's i possibilitat de comunicació a doble velocitat

- Suporta diferents formats de protocol: de 5 fins a 9 bits, amb paritat o no i amb 1 o 2 bits de stop

- Detecció d'errors

- Possibilitat d'emprar la interrupció com a mitjà de millorar la transmissió/recepció

La figura 1 mostra un esquema simplificat de l'arquitectura de la UART. S'hi observen clarament tres mòduls diferenciats: el mòdul de transmissió amb el pin de sortida TxD (situat en el PORTB.0), el mòdul de recepció a través del pin RxD (que es troba en PORTB.1) i el mòdul de sincronisme amb el pin de rellotge XCK emprat només en comunicació síncrona.

Figura 1. Arquitectura de la USART

El mòdul de transmissió disposa del seu registre de desplaçament, lògica de control i de generació de paritat i d'un buffer d'escriptura que li permet efectuar la transmissió contínua de paraules sense retards enmig.

El mòdul de recepció conté la lògica de sincronisme en recepció asíncrona, un registre de desplaçament, lògica de control i de paritat i un doble buffer de recepció que li permet operar com a FIFO i donant-li una major seguretat en la recepció de dades.

La USART és un mòdul de certa complexitat en el microcontrolador i necessita una lectura acurada del full d'especificacions. Per això, en el que segueix només es comenten els aspectes principals del seu control a través dels registres de configruació.

- Registre d'E/S de la USART, UDR. Els buffers de transmissió i de recepció comparteixen la mateixa adreça d'E/S, UDR. El buffer de transmissió és el buffer on es posa la dada a enviar i el de recepció és el d'arribada de dades en la recepció.

- Registre A de status i control, UCSRA. Com en el comptador 0 és el registre d'activació d'interrupció dels comptadors. Els bits que afecten al comptador1 són:

Bit 0 - MPCM. Habilita la comunicació multiprocessador

Bit 1 - U2X. Bit de duplicació de velocitat de transmissió

Bit 2 - PE. Parity Error. Es posa a 1 quan hi ha (i s'ha programat) error de paritat

Bit 3 - DOR. Data overRun. Es posa a 1 quan el buffer de recepció queda ple.

Bit 4 - FE. Frame Error. S'activa en detectar un error de bit de stop.

Bit 5 - UDRE. USART data register empty. Quan és 1 indica que el buffer de transmissió és buit i pot rebre una nova dada. Pot generar la interrupció UDRIE.

Bit 6 - TXC. USART Transmit Complete. Es posa a 1 quan s'ha enviat tot el frame. S'esborra de forma automàtica en entrar en la rutina de servei TXCIE.

Bit 7 - RXC. USART Receive Complete. Es posa a 1 quan hi ha una dada no entrada en el buffer i es posa a 0 en llegir-la. Pot generar una interrupció RXCIE.

- Registre B de status i control, UCSRB. Com en el comptador 0 és el registre d'activació d'interrupció dels comptadors. Els bits que afecten al comptador1 són:

Bit 0 - TXB8. És el 9è bit de transmissió quan es treballa amb 9 bits

Bit 1 - RXB8. És el 9è bit de recepció quan es treballa amb 9 bits

Bit 2 - UCSZ2. Va amb els bits UCSZ1:0 del registre UCSRC.

Bit 3 - TXEN. Habilita la transmissió en la USART

Bit 4 - RXEN. Habilita la recepció en la USART

Bit 5 - UDRIE. S'habilita la interrupció sobre el flag UDRE

Bit 6 - TXCIE. Habilita la interrupció sobre el flag de transmissió TXC

Bit 7 - RXCIE. Habilita la interrupció sobre el flag de recepció RXC

- Registre C de status i control, UCSRC. Com en el comptador 0 és el registre d'activació d'interrupció dels comptadors. Els bits que afecten al comptador1 són:

Bit 0 - UCPOL. Configuració del rellotge en comunicació síncrona. A zero en comunicació asíncrona

Bit 2:1 - UCSZ1:0. Juntament amb UCSZ2 (UCSRB), UCSZ2:0 estableix el nombre de bits en la comunicació. Quan val 3 s'envien 8 bits.

Bit 3 - USBS. Indica el nombre de bits de stop. Quan és zero indica 1 bit

Bit 5:4 - UPM1:0. Estableix la paritat. A 0 quan no s'empra paritat.

Bit 6 - UMSEL. A 0 indica comunicació asíncrona (tal es fa servir en aquesta pàgina)

Bit 7 - URSEL. Veure URSEL en registre UBBRH. Quan és 1 selecciona el registre UCSRC

- Registres de baud rate, UBRRH i UBRRL. És el registre que estableix el baud rate de comunicació, que agafa els bits UBRR[11:0], els quatre primers es troben en el UBBRH i la resta:

Bit 11-0 - UBRR11:0. Són els bits d'establiment de la velocitat de comunicació. UBRRH conté els 4 bits més significatius mentre que UBRRL en conté els menys significatius.

Bit 15 - URSEL. És un bit complicat! com que UBBRH comparteix adreça d'E/S amb UCSRC. Ha de ser 0 quan s'escriu a UBRRH.

La velocitat de transmissió depèn del baud rate seleccionat, de si s'ha activat el bit de comunicació de doble velocitat i de la freqüència de rellotge base del microcontrolador. Per això, per establir la velocitat de comunicació cal consultar les taules del manual d'especificacions.

Com a exemple i posat la velocitat de comuncicació a normal (U2X=0), es tenen les següents velocitats de transmissió (en cada cas, consultar l'error introduït en la taula del microcontrolador):

BaudRate UBRR(fosc=1MHz) UBRR(fosc=8MHz) UBRR(fosc=16MHz) 2400

4800

9600

19200

38400

57600

76800

115200

250000

50000025

12

6

2

1

0

-

-

-

-207

103

51

25

12

8

6

3

1

0

207

103

51

25

16

12

8

3

1

Codificació en negreta significa millors precisió en la transmissió

Funcionament de la USART

Inicialització

Abans de realitzar cap comunicació la USART s'ha d'inicialitzar. La inicialització inclou l'establiment del baud rate, posar el format de transmissió (nombre de bits, paritat, bits de stop) i l'habilitació de la transmissió i recepció i si es fa per interrupcions.

Un codi exemple base de comunicació pot ser:

;-------RUTINA DE SETUP DE LA UART------------------------------------

; a 4800 bauds i frame format: 8data,1stop bit

setup_UART:

ldi temp0,0 ;baud rate a 4800

out UBRRH,temp0

ldi temp0,12

out UBRRL,temp0

ldi temp0,(1<<RXEN)|(1<<TXEN) ;enable recepció i transmissió

out UCSRB,temp0

ldi temp0,(1<<URSEL)|(1<<UCSZ1)|(1<<UCSZ0) ;frame format: 8 bits, 1 stop, no paritat

out UCSRC,temp0

ret

Funcionament de la transmissió

La transmissió s'habilita a través del bit TXEN del registre UCSRB. La seva habilitació sobreseu el funcionament del bit PORTD.1 que passa a ser el pin de sortida de la transmissió, TxD.

La transmissió s'inicia carregant el buffer de transmissió (escriptura al registre d'entrada/sortida UDR) amb la dada a transmetre. La dada s'enviarà al registre de desplaçament per a ser enviada un cop aquest estigui lliure (immediatament si no té cap dada, o un cop hagi transmès la dada que té).

Per tant, si no es vol perdre cap dada en la transmissió, no es pot enviar lliurement una dada al buffer de transmissió, si no que s'ha d'esperar a què estigui lliure. Això es pot conèixer per polling o per interrupció.

L'exemple mostra una rutina de polling sobre el buffer UDR preguntant pel bit UDRE, USART Data Register Empty.

;-------RUTINA DE TRANSMISSIÓ-----------------------------------------

;Molt senzillament, aquesta rutina envia un byte cada cop que es crida

;No es pot enviar fins que el registre de trasmissió queda buit

transmit: sbis UCSRA, UDRE

rjmp transmit

out udr, dada

ret

Evidentment l'ús de la rutina de polling pot significar importants retards de procés quan hi ha moltes dades per enviar. En aquests casos, quan no n'hi ha prou incrementant al màxim permès la velocitat de transmissió, és recomanable emprar una cua i interrupcions per conèixer si una nova dada pot ser carregada al buffer de transmissió.

Funcionament de la recepció

El funcionament de la recepció és similar al de transmissió. La recepció s'habilita a través del bit RXEN del registre UCSRB. La seva habilitació sobreseu el funcionament del bit PORTD.0 que passa a ser el pin d'entrada de la recepció, RxD.

La recepció s'inicia quan detecta un bit de recepció vàlid. Cada nou bit que es reb es va carregant en el registre de desplaçament de recepció fins que es reb el primer bit de stop, moment en què passa la dada al buffer de recepció. Llegint el registre d'E/S UDR es carrega la dada en el regsitre pertinent.

L'exemple mostra una rutina de polling sobre el bit RXC per determinar si ha arribat una nova dada. El flag RXC es manté activat mentre no es llegeix la dada del registre UDR.

;-------RUTINA DE RECEPCIÓ-----------------------------------------

;Molt senzillament, aquesta rutina espera l'arribada d'una dada

;Aleshores la carrega en el registre temporal

recepcio: sbis UCSRA, RXC

rjmp recepcio

in temp, udr

ret

El document Ús de la USART és una introducció a l'ús de la USART del ATmega8 i l'hyperterminal com a eina per a la depuració de programes.