Ejemplo: Implementar el código VHDL correspondiente al circuito

sentencias concurrentes

Para la declaración y asignación de señales se utiliza

el operador <=

Recordad que, a diferencia de la asignación de señales, la asignación de variables utiliza el operador igualdad

Instrucción When - Else

Instrucción de slección de valor

Formato: <señal> <= <valor> when <comparación> else <valor>;

Ejemplo: multiplexor de 1 entrada de control

Instrucción With - Select

Permite la enumeración de todas las posibles elecciones

del conjunto de entradas

Uso de when...others para agrupar conjunto de salidas comunes

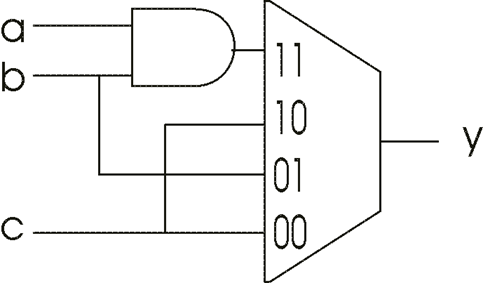

Ejemplo: Implementar el código VHDL correspondiente al circuito

Instrucción Process

Concepto concurrente para describir hardware (que debe ejecutarse

concurrentemente) mediante instrucciones secuenciales

Aunque internamente las instrucciones se ejecuten secuencialmente, como bloque

es una instrucción concurrente

Instrucción Block

Cumple, principalmente, tres funciones:

Estructura el código

Realiza asignaciones guardadas

Describe la jerarquía

A pesar de sus funciones, a menudo se divide el código entre ficheros antes que utilizar esta instrucción

Sintaxis

<etiqueta>:block [<expresion guarda>] [is]

[generic (<lista de genéricos>);

[generic map (<lista de asociación>);]]

[port (<lista de puertos>);

[port map (<lista de asociación>);]]

{<parte declarativa}

begin

{<sentencias concurrentes>}

end block [<etiqueta>];