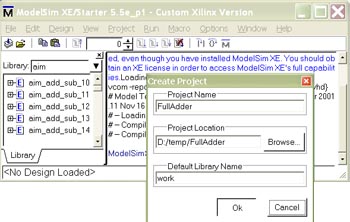

Pera crear un proyecto, se ejecuta Modelsim.

Al abrirse la ventana de Modelsim se elige la opción File-> New -> Project. Se elige el directorio de trabajo y se da nombre al proyecto

La ventana principal de Modelsim, creando el proyecto, tiene este aspecto:

El Modelsim se utiliza introduciendo comandos en la subventana de la derecha o utilizando menús desplegables.

El siguiente paso es incluir el fichero VHDL en el proyecto. Para ello existen dos opciones:

- Se accede al menú Project -> Add file to project y se copian los ficheros en la carpeta del proyecto (así quedan los códigos fuente en la misma carpeta)

- Se elige Project -> New -> Source -> VHDL. Entonces se abre la ventana de edición de código en la que se crea el nuevo código fuente. Una vez introducido el código fuente en la ventana de edición (source_edit) se guarda el proyecto en el propio directorio de trabajo que sale al abrirse el menú de guardar código fuente: File -> Save as -> y se introduce el nombre del fichero FullAdder.vhd (la extensión es importante!))

Creado el código fuente se compila. La compilación indica si se han producido errores sintácticos o léxicos en la creación del código. Puede realizarse:

- Eligiendo en la propia ventana de edición de código File -> Compile o pulsando el botón de compilación de la ventana.

- Desde la ventana principal de Modelsim eligiendo Design -> Compile o pulsando el botón de compilación de la ventana.

Se abre la ventana de compilación y se elige el fichero a compilar. En la ventana sólo aparecen los ficheros .vhd. Por ello es importante guardar la extensión al dar nombre al código fuente puesto que si no ¡no se verá fichero alguna para compilar!

Simulación del proyecto

Los diseños compilados se encuentran en la librería .work.

Para poder relizar la simulación hay que cargarlos: Design->

Load design->FullAdder->Load.

Para iniciar una simulación se aconseja abrir todas las ventanas del Modelsim: View->All. Las ventanas abiertas son:

• Source: Muestra el código del diseño a simular. Para poder editar el código se debe desbloquear: Edit->Read only

• Signals: Lista de señales del código VHDL

• Variables: Lista de variables utilizadas en el código VHDL

• Process: Ventana de indicación de seguimiento del proceso

• Dataflow: Representación gráfica del flujo de datos en el diseño. Clickando sobre las señales se puede navegar a través de los distintos procesos del diseño.

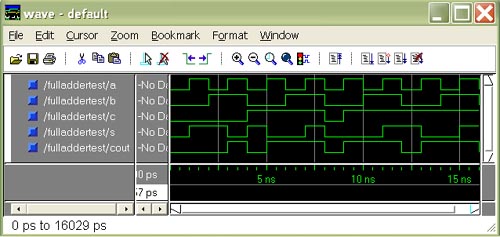

• Wave: Ventana para la presentación de los estados de las señales como formas de onda.

• List: Ventana de seguimiento de eventos de la simulación.

(Puesto que nuestro código, por el momento es simple, podemos dejar sólo las ventanas Signals y Wave)

Accediendo a las ventanas de señales y variables podemos seleccionar aquellas señales y variables que deseamos ver en las ventana Wave y List. En este caso, puesto que sólo tenemos señales, las podemos ver en la ventana Wave clickando en la ventana Signals, View -> Wave -> Signals in region

El paso siguiente consiste en dar los valores a las entradas para validar el modelo. En diseños sencillos es común forzar los valores de las señales a mano. Para ello se selecciona una señal (en la ventana Signals) y se elige Edit -> Force. Si se quiere forzar un señal de reloj debe elgirse la opción Clock.

En nuestro caso puede ser conveniente elegir una señal de reloj para cada variable, a frecuencia doble cada una de ellas. Por ejemplo, se pueden elegir a 1000 (corresponde a 1 ns), 2000 (es decir, 2 ns) y 4000 (para 4 ns). esto es debido a que el tiempo base utilizado por defecto (a menos que lo cambiemos) se basa en ps.

Una vez elegida la señal de relog debemos establecer el tiempo de simulación que se desea ejecutar a cada paso. Si se quieren ejecutar pasos de 1 ns de simulación se debe introducir 1000 en el cuadro de diálogo Run length (significa 1000 ps) de la ventana principal de Modelsim. Entonces, a cada click de la opción Run (ventana principal o venana Wave) se realiza una simulación que dura 1 ns.

También puede darse la orden de ejecución de un determinado tiempo de simulación (por ejemplo 10 ns) escribiendo la lína de comando

>run 10 ns

En la ventana Wave puede comprobarse si las salidas tienen los valores correctos.

La opción de simulación Restart reinicializa todos los valores de la simulación, por lo que de ejecutarse deben volverse a introducir todos los parámetros de las señales.

Para evitar ello existen dos opciones:

• Realizar un log de las acciones ejecutadas durante la simulación (eligiendo dicha opción desde la ventana principal)

• Realizar un modelo de test (utilizando VHDL) del modelo implementado.

En el apartado siguiente se detalla esta última opción por ser muy práctica y altamente recomendada. Aunque inicialmente pueda parecer más tediosa a la larga resulta muy práctica, especialmente cuando se desarrollan modelos complejos.