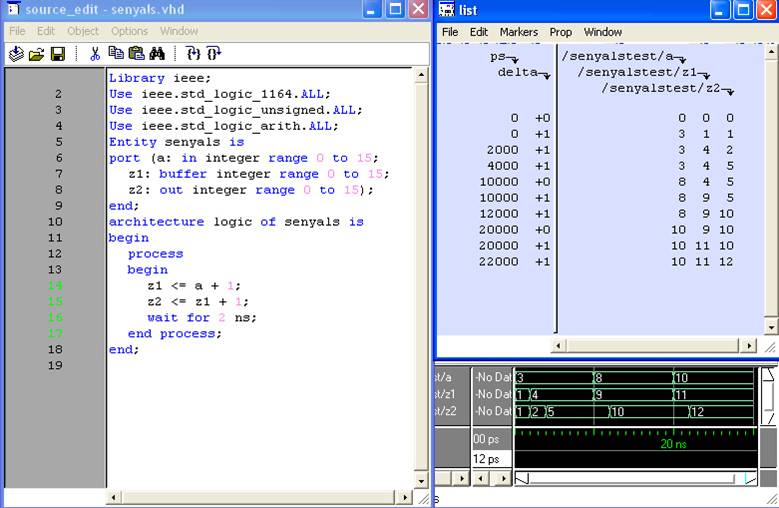

La siguientes figuras muestran resultados de simulación sobre un circuito con el que se trabaja, primero con señales, después con variables

El circuito modelado representa el incremento de dos variables encadenadas

Para conocer mejor las transacciones que se producen durante la simulación se ha abierto la ventana List del Modelsim

List es una ventana que se puede abrir cuando se ha cargado un modelo compilado para simulación. Muestra un listado de todas las transacciones sobre señales y variables que se producen durante la simulación

Trabajando con señales

Este primer modelo trabaja con señales

En la simulación se ha introducido un tiempo de espera de 2ns para poder obsevar mejor la evolución de las señales

Tiempo 0: Las señales se inicializan a 0, a debe tomar su primer valor (igual a 3). Tras un retardo elemental, la evolución de las señales las lleva a: a=3, b=1, c=1 (b y c parten de que a vale, por inicialización, 0)

Tiempo 2 ns: a no cambia. Primero evoluciona z1 y, después de un retardo, evoluciona z2. Es un símil de lo que ocurre durante la evolución de un circuito combinacional

Tiempo 10 ns: Se produce un cambio en a y z1 y z2 evolucionan, después de un respectivo retardo elemental, a sus nuevos valores

Puede observarse que, como se tienen dos señales conectadas en serie, se necesitan dos retardos elementales para su evolución

Trabajando con variables

Se ha utilizado el mismo modelo pero trabajando ahora con variables

Puede observarse como el resultado pasa a ser el mismo. Sin embargo, debido a que dentro de un proceso concurrente las variables se actualizan al mismo tiempo, no existe la propagación de señales (debido a retardos elementales encadenados) como en el caso de trabajar coon señales

Conclusiones

El modelado VHDL de circuitos permite trabajar internamente con señales y con variables

Cuando se trata de circuitos combinacionales los resultados finales...

...en simulación, son los mismos pero pueden obtenerse en tiempos distintos

...en síntesis, puesto que no ha lugar la consideración de retardo elemental, se obtiene el mismo diseño

Sin embargo, debe cuidarse el uso de señales y/o variables cuando se trabaja con circuitos secuenciales. Puesto que se trabaja con señales sincronizadas por reloj puede darse el caso que el resultado se obtenga en un ciclo de reloj posterior al esperado