Patrón de verificación a partir de tabla funcional

A menudo la generación de una tabla de comportamiento permite visualizar de forma más fácil las formas de onda que se aplican al modelo

Para introducir esta tabla de comportamiento en el modelo de verificación es conveniente crear un registro de datos que, en primera instancia, va a contener la evolución (forma de onda) de las señales de entrada en forma de tabla de verdad

Posteriormente, la arquitectura ejecuta el envío de los datos almacenados en la tabla de verdad hacia las entradas del DUT con el objeto de comprobar el funcionamiento del DUT

Ejemplo

El siguiente modelo VHDL muestra un posible código

que comprueba el contador

Para el desarrollo de este código hay que tener presente:

- En la definición del registro, detallar correctamente las entradas (no tienen por qué ser todas) a las que se va a aplicar la forma de onda por tabla de verdad

- ¡Cuidado con la instrucción que se usa para generar la tabla!

type array_test is array (natural range <>) of mostra;

La expresión natural range <> implica que el compilador no conoce el total de vectores a aplicar hasta que ha leído la totalidad de la tabla. Esta expresión está permitida por que la tabla se define como una constante

- Dentro del proceso debe establecerse el orden que se sigue para leer la tabla. Suele ser adecuado utilizar la instrucción for...loop, cuyo avance se suele sincronizar al ciclo de reloj

- ¿Qué señales deben colocarse dentro de la tabla de verdad? ¿Es conveniente que el reloj esté en la tabla de verdad? Depende del modelo a aplicar, y la práctica nos suele indicar qué método suele ser el más simple. Trabajando con circuitos secuenciales simples, generar automáticamente el reloj (no introducirlo en la tabla de verdad) suele agilizar la creación de la tabla de test

- Hay que fijarse bien en el sincronismo de las entradas y las salidas esperadas. Debemos recordar que todo proceso queda pendiente hasta que una señal provoca el evento. En este caso, el evento lo produce el flanco negativo de reloj. ¿Como funciona, pues, todo el proceso?

· Primero se activan (en el modelo de test) las señales a aplicar al DUT

· Al llegar el flanco negativo del reloj, se propagan estas señales a las entradas del DUT

· Estas señales van a controlar la evolución del contador cuando llegue el flanco positivo del mismo (del cual depende el cambio de estado en el contador)

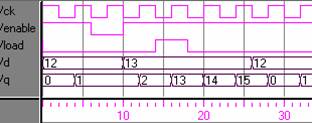

El resultado de la verificación del contador en este caso viene dado en la siguiente gráfica

Una mejora al test mediante tabla de verdad puede introducirse realizando una verificación de código de forma 'automática'

En el caso del contador puede realizarse introduciendo una señal más en la tabla: la salida esperada, que en este caso es el estado esperado. Entonces, la aplicación de los vectores de verificación se realiza esperando que la salida del DUT se corresponda con la salida esperada. Mediante una señal de comparación de ambas salida se conoce inmediatamente si el modelo actúa de forma correcta

Ejemplo

El siguiente modelo VHDL muestra un posible código

autoverificable que comprueba el contador

En la tabla de verificación se han introducido salidas esperadas erróneas para que se comprenda mejor la aplicación del método

El gráfico siguiente muestra la salida obtenida en este caso. Puede comprobarse como las salidas erróneas (en la señal okq) se producen exactamente en los vectores de test que expresamente se han introducido de forma erróna