Codificación de estados

En casos determinados suule ser necesario introducir una codificación de estados determinada.Esto puede realizarse definiendo constantes de tipo estado. Entonces, la variable tipo estado sólo evolucionará dentro de las constantes predefinidas

Ejemplo

entity mefEnum is

port(ck: in bit;

z: out bit);end;

architecture f of mefEnum is

type estado is array (2 downto 0) of bit; -- Definición de estados

constant s0: estado:="001"; -- Codificación de los estados

constant s1: estado:="010";

constant s2: estado:="100";

signal s: estado:= s0; -- Variable tipo estado

beginprocess

beginwait until ck='1';

case s iswhen s0 => s <= s1;

when s1 => s <= s2;

when others => s <= s0;end case;

end process;

z <= '1' when s=s2 else '0';end;

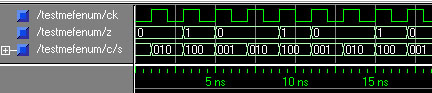

Entonces, la codificación de los estados vendría determinada por el código VHDL escrito. La siguiente gráfica muestra la correspondiente simulación

|

|