Ejemplo: latch SR.

El latch SR, bajo una determinada entrada, tiene las salidas Q i nQ iguales, motivo por el que, en esta circunstancia, no actua como biestable. Esta inconsistencia puede ser documentada mediante la instrucción Assert

El código siguiente muestra una forma de documentarlo:

El modelo de test se encuentra en

En el modelo del latch se han introducido retardos para provocar violaciones de la aserción

La instrucción assert utiliza el atributo señal'image(señal). Su misión es crear una imagen de la señal e imprimirla. De esta forma no se interacciona sobre la misma

Nota: El atributo 'image está definido en el VHDL'93

Notas sobre el ejemplo:

En la aserción se consideran correctos dos casos:

El caso Q=not(nQ). Es el funcionamiento típico de un biestable

En el tiempo inicial t=0 fs. Al iniciarse la simulación se cumple esta condición temporal. Por consiguiente no se detecta (warning) que Q y nQ son iguales (que durante la inicialización del instante inicial puede ocurrir)

Puesto que la incidencia es un fallo normal del latch se documenta como warning, advirtiendo que no debería pasar

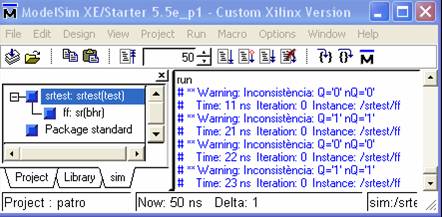

Al correr la simulación se puede comprobar que assert se activa a los 11 ns debido al retardo de simulación impuesto en el modelo: durante 1 ns Q=nQ y, ello, activa la condición de error

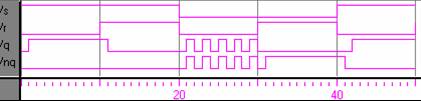

La siguiente figura muestra el resultado de la simulación. En ella se pueden observar todos los comentarios anteriores

|

|

|

- Si continuamos ejecutando la simulación, ¿que

ocurre (a los 20 ns)? Expresamente se ha puesto un wait de espera

en la ejecución del programa de test igual al retardo en la propagación

de señales del latch. Con ello se provocan retardos de simulación

idénticos a los retardos de propagación, motivo por el que el

simulador entra en un bucle de resultados oscilatorio. Con tiempos de simulación

adecuados, esta oscilación desaparece. Probar

de cambiar el tiempo de espera de la instrucción wait (0.1,

0.5, 2, 5, ... ns)